QR 코드

문의하기

팩스

+86-579-87223657

주소

중국 절강성 진화시 우이현 쯔양 거리 왕다로

반도체 제조 산업에서 장치 크기가 계속 줄어들면서 박막 재료의 증착 기술은 전례없는 과제를 제기했습니다. 원자 수준에서 정확한 제어를 달성 할 수있는 박막 증착 기술로서 원자 층 증착 (ALD)은 반도체 제조의 필수 부분이되었다. 이 기사는 ALD의 프로세스 흐름과 원칙을 소개하여 중요한 역할을 이해하는 데 도움이됩니다.고급 칩 제조.

1알드프로세스 흐름

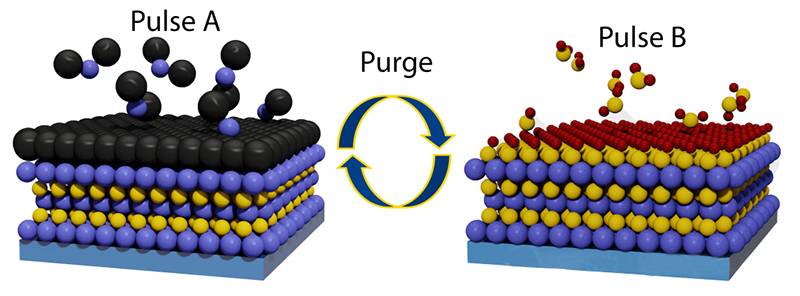

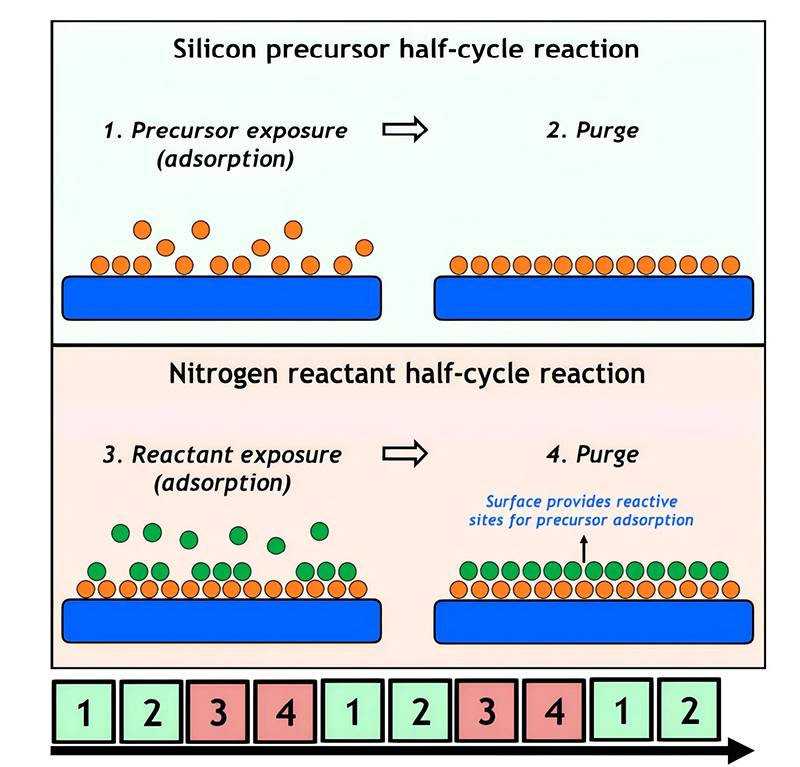

알드 공정은 엄격한 시퀀스를 따릅니다. 이는 하나의 원자 층만이 퇴적 할 때마다 첨가되어 필름 두께의 정확한 제어를 달성합니다. 기본 단계는 다음과 같습니다.

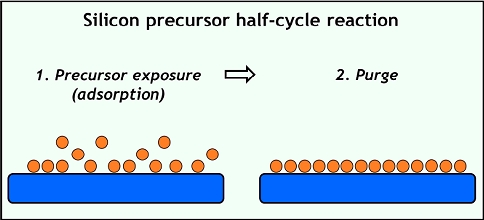

전구체 펄스 : the알드프로세스는 첫 번째 전구체를 반응 챔버로 도입하는 것으로 시작됩니다. 이 전구체는 표적 증착 재료의 화학 요소를 함유하는 가스 또는 증기입니다.웨이퍼표면. 전구체 분자는 웨이퍼 표면에 흡착되어 포화 분자 층을 형성한다.

불활성 가스 퍼지 : 그 후, 불활성 가스 (예 : 질소 또는 아르곤)가 반응되지 않은 전구체 및 부산물을 제거하기 위해 퍼지를 위해 도입되어 웨이퍼 표면이 깨끗하고 다음 반응을 위해 준비되도록합니다.

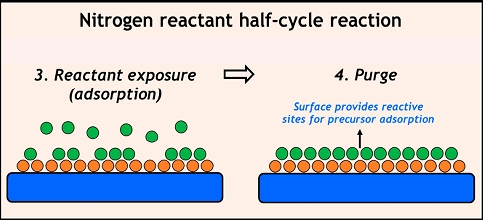

두 번째 전구체 펄스 : 퍼지가 완료된 후, 제 2 전구체는 첫 번째 단계에서 흡착 된 전구체와 화학적으로 반응하여 원하는 침착 물을 생성합니다. 이 반응은 일반적으로 자기 제한입니다. 즉, 모든 활성 부위가 첫 번째 선구자에 의해 점유되면 새로운 반응이 더 이상 발생하지 않습니다.

비활성 가스 퍼지 다시 : 반응이 완료된 후, 불활성 가스를 다시 정화하여 잔류 반응물 및 부산물을 제거하고 표면을 깨끗한 상태로 회복시키고 다음 사이클을 준비합니다.

이 일련의 단계는 완전한 ALD 사이클을 구성하며 사이클이 완료 될 때마다 원자 층이 웨이퍼 표면에 추가됩니다. 사이클 수를 정확하게 제어함으로써, 원하는 필름 두께가 달성 될 수있다.

(ALD 1 사이클 단계)

2. 프로세스 원리 분석

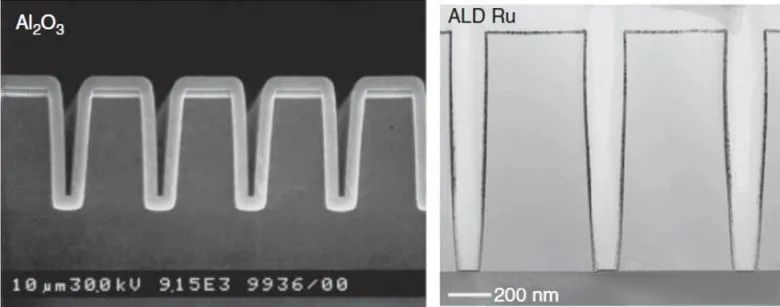

알드의 자기 제한 반응은 핵심 원칙입니다. 각 사이클에서, 전구체 분자는 표면의 활성 부위와 만 반응 할 수있다. 일단 이들 부위가 완전히 점유되면, 후속 전구체 분자는 흡착 될 수 없으므로, 각 증착 라운드에서 하나의 원자 또는 분자 만 첨가되도록한다. 이 기능은 ALD가 박막을 퇴적 할 때 매우 높은 균일 성과 정밀도를 갖습니다. 아래 그림과 같이 복잡한 3 차원 구조에서도 우수한 단계 커버리지를 유지할 수 있습니다.

3. 반도체 제조에서 ALD의 적용

알드는 다음을 포함하되 이에 국한되지 않는 반도체 산업에서 널리 사용됩니다.

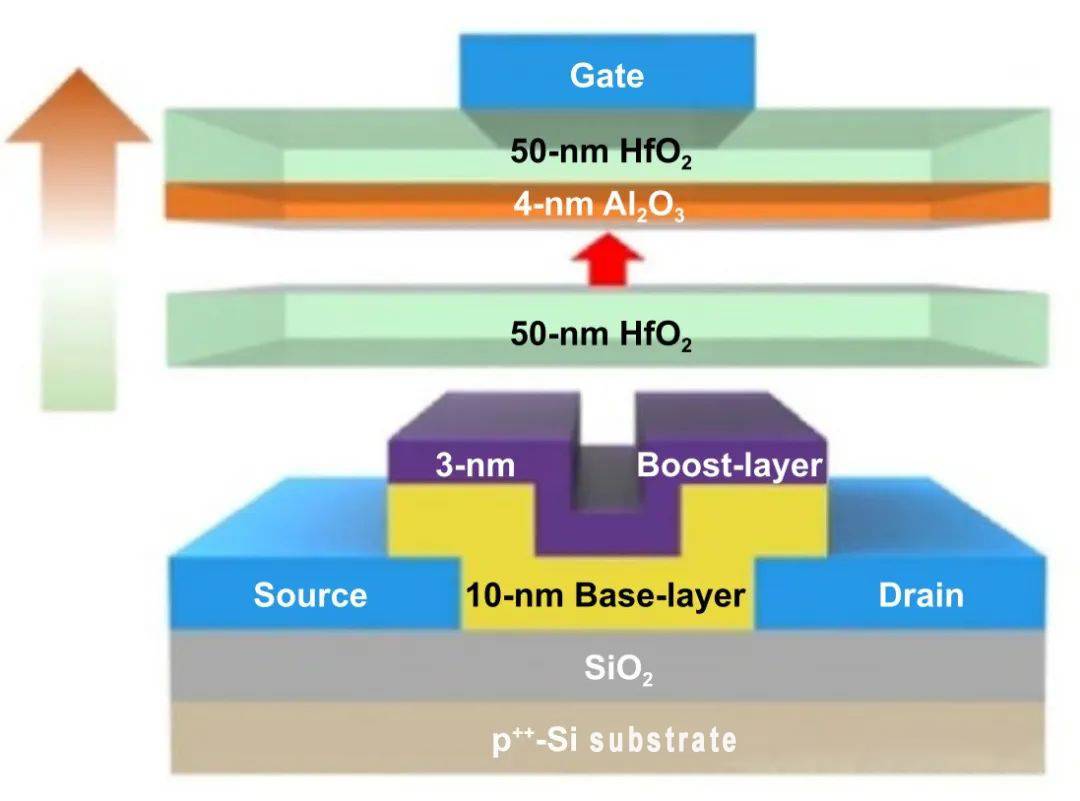

High-K 재료 증착 : 장치 성능을 향상시키기 위해 새로운 세대 트랜지스터의 게이트 절연 층에 사용됩니다.

금속 게이트 증착 : 트랜지스터의 스위칭 속도 및 효율을 향상시키는 데 사용되는 질화 티타늄 (TIN) 및 탄탈 룸 (TAN)과 같은 금속 게이트 증착.

상호 연결 장벽 층 : 금속 확산을 방지하고 회로 안정성 및 신뢰성을 유지합니다.

3 차원 구조 충전 : 더 높은 통합을 달성하기 위해 FinFET 구조의 채널 채널과 같은.

원자 층 증착 (ALD)은 특별한 정밀성과 균일 성으로 반도체 제조 산업에 혁신적인 변화를 가져 왔습니다. ALD의 프로세스와 원칙을 마스터함으로써 엔지니어는 나노 스케일에서 우수한 성능을 가진 전자 장치를 구축하여 정보 기술의 지속적인 발전을 촉진 할 수 있습니다. 기술이 계속 발전함에 따라 ALD는 미래의 반도체 분야에서 더욱 중요한 역할을 할 것입니다.

+86-579-87223657

중국 절강성 진화시 우이현 쯔양 거리 왕다로

저작권 © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. 모든 권리 보유.

Links | Sitemap | RSS | XML | 개인 정보 보호 정책 |